#### **Digital computation**

# Logic design with FPGAs

Synchronous logic and logic synthesis BASYS2 FPGA board Spartan FPGA Xilinx ISE WebPACK Verilog & Gateway "HelloWorld" exercise

albruck. Electronics for Physicists II (Digital

2. Bit-perfect deterministic logical state

T. Delbruck, Electronics for Physicists II (Digital)

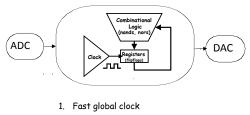

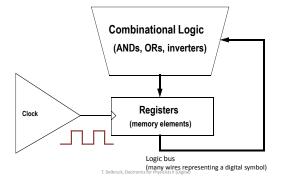

### Synchronous logic

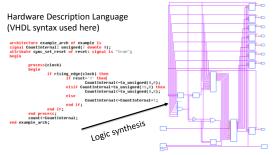

### How logic is designed now

By using HDLs, industry can design complex chips with >100 million logic elements T. Debruck, Electronics for Physicists II (Digital)

#### Field Programmable Gate Arrays (FPGAs)

- Reconfigurable logic chips with lots of registers, compared with **CPLD**s and **PAL**s.

- Range in price from \$10 to \$10,000 per chip depending on number of "gate equivalents".

- They do not provide you a processor with instructions, ALU and memory (although you can embed a processor in a larger FPGA).

- Sold by Xilinx, Altera, Lattice, Actel, etc

CPLD = Complex Programmable Logic Device PAL = Programmable Array Logic

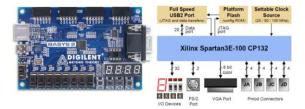

### BASYS2 FPGA board Xilinx Spartan 3E XCS100E

. . . . . . . .

- Xilinx Spartan 3-E FPGA, 100K or 250K gate

- · FPGA features 18-bit multipliers, 72Kbits of fast dual-port block RAM, and 500MHz+ operation

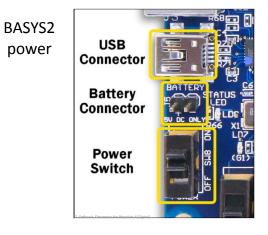

- USB 2 full-speed port for FPGA configuration and data transfers (using Adept 2.0 software available as a free download)

- · XCF02 Platform Flash ROM that stores FPGA configurations indefinitely

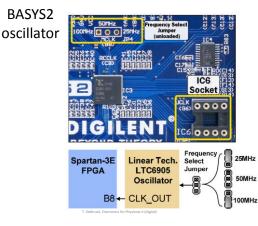

- User-settable oscillator frequency (25, 50, and 100

- MHz), plus socket for a second oscillator Three on-board voltage regulators (1.2V, 2.5V, and 3.3V) that allow use of 3.5V-5.5V external supplies

- 8 LEDs, 4-digit seven-segment display, four pushbuttons, 8 slide switches, PS/2 port, and a 8-bit VGA port

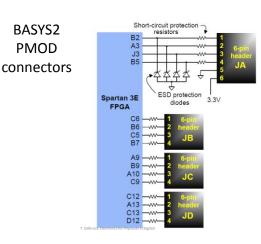

- · Four 6-pin headers for user I/Os, and attaching Digilent PMOD accessory circuit boards

## **BASYS2 IO**

| Products            | Support           | Classroom                                                                                                                                                                                              | Services                             | Showcase                     | About Us | My Cart 🦮   |

|---------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------|----------|-------------|

| Pmod <sup>™</sup> P | eripheral Modules |                                                                                                                                                                                                        |                                      |                              |          |             |

|                     |                   | modWiFi - 802.1                                                                                                                                                                                        |                                      | terface                      | \$59.99  | Add to Cart |

|                     |                   | Serialized unique MAC a                                                                                                                                                                                |                                      |                              |          | More Info   |

|                     | . pr :            | 1 and 2Mbps data rates EEE 802.11kgin-compatible Integrated PCB antenna Range: up to 400m (1300 ft.)                                                                                                   |                                      |                              |          |             |

| Pm                  | od <u>we</u> r.   | Radio regulation certifica<br>Wi-Fi certified (WFA ID: )                                                                                                                                               | tion for the United Stat<br>WFA7150) | tes (FCC), Canada (IC), Eur  |          |             |

| INPUT/O             |                   | modBT - Blueto                                                                                                                                                                                         |                                      | ent serial cable replacement | \$54.99  | Add to Cart |

| 1                   | Con I             | mode or a more powerful command mode<br>• Wide range of profiles including generic access profile, service discovery profile, a                                                                        |                                      |                              |          | More Info   |

| Pmod                |                   | s serial port profie<br>Simple UAPT Interface<br>2.5% – 3.6% operating voltage<br>• Small size (5% 1.5%)<br>Ships with a UART crossover cable, a 6° 12.pin cable, a 6° 2x6.pin to dual 6.pin cable, or |                                      |                              |          |             |

|                     |                   | and two 6-pin headers                                                                                                                                                                                  |                                      |                              |          |             |

|                     |                   | 10 Mb/s IEEE 802.3 com                                                                                                                                                                                 |                                      |                              | \$29.99  | Add to Cart |

|                     |                   | SPI interface                                                                                                                                                                                          |                                      |                              |          | More info   |

### Spartan architecture

#### Spartan 3 XC3S100E

Table 2: Available User I/Os and Differential (Diff) I/O Pairs

| Package   | VQ<br>VQC | 100<br>6100      | CP132<br>CPG132   |           |   | TQ144<br>TQG144 |                  | PQ208<br>PQG208 |     |

|-----------|-----------|------------------|-------------------|-----------|---|-----------------|------------------|-----------------|-----|

| Size (mm) | 16 )      | c 16             | 8 :               | x 8       |   | 22 x 22         |                  | 28 x 28         |     |

| Device    | User      | Diff             | User              | Diff      |   | User            | Diff             | User            | Dif |

| XC3S100E  | 66<br>(7) | <b>30</b><br>(2) | <b>83</b><br>(11) | 35<br>(2) |   | 108<br>(28)     | <b>40</b><br>(4) | -               | -   |

|           |           |                  |                   |           | Γ | 100             | ••               |                 |     |

T. Delbruck, Electronics for Physicists II (Digital)

### Device datasheet (233 pages...)

| XILINX <sup>®</sup>                                                                                                                                                                                                                                                                            | Spartan-3E FPGA Family:<br>Data Sheet                                                                                                                                                                                                                                                                                                                |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| DS312 (v3.8) August 26, 2009                                                                                                                                                                                                                                                                   | Product Specification                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Module 1:<br>Spartan-3E FPGA Family: Introduction<br>and Ordering Information<br>DS312-1 (v.8) August 26, 2009<br>Introduction<br>- Reatures<br>- Architectural Overview<br>- Package Marking<br>- Ordering Information<br>Module 2:<br>Functional Description<br>DS3122 (v.8) August 26, 2009 | Module 3:<br>DC and Switching Characteristics<br>D5312-3 (v3.8) August 26, 2009<br>D C Electrical Characteristics<br>- Absolute Maximum Ratings<br>- Supply Votage Specifications<br>- D C Characteristics<br>- D C Characteristics<br>- WO Timing<br>- SUGE Timing<br>D CCM Timing<br>- Block RAM Timing<br>- Block RAM Timing<br>- Witchier Timing |  |  |  |

XC3S100E package 0 10 I/O: Ur VREF: User I/O or 16 to 22 7 to 8 UAL VCCO: Output CLK: User I/O, input, or glo 0 to 3 16 8 CONFIG: Dedica JTAG: D ed JTAG port VCCINT: I 2 4 6 n pins tage (+1.2V) N.C.: Und GND: Ground VCCAUX: Auxil voltage (+2.5V) cted balls on FPGA (�)

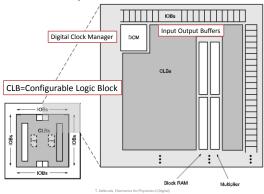

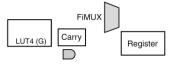

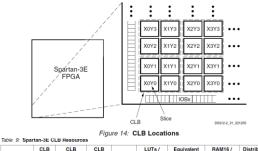

### **CLB** structure

- Each CLB has 4 slices

- Each slice has 4-input LUT (look-up table) logic block and single bit latch (register), plus multiplexors, shift registers, carry bits, RAM, etc.

- One slice simplified: The LUT is programmed to compute any desired logic function of 4 inputs.

• Generally you don't need to know about this; just to be aware of what fabric your synthesized logic is finally mapped to.

T. Delbruck, Electronics for Physicists II (Digital

CLBs (Config. Logic Blocks)

| Device   | CLB<br>Rows | CLB<br>Columns | CLB<br>Total <sup>(1)</sup> | Slices | LUTs /<br>Flip-Flops | Equivalent<br>Logic Cells | RAM16 /<br>SRL16 | Distributed<br>RAM Bits |

|----------|-------------|----------------|-----------------------------|--------|----------------------|---------------------------|------------------|-------------------------|

| XC3S100E | 22          | 16             | 240                         | 960    | 1,920                | 2,160                     | 960              | 15,360                  |

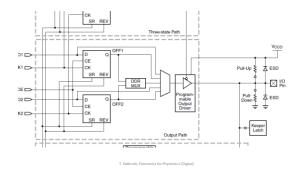

### Spartan IOB structure (part) (Input Output Buffer)

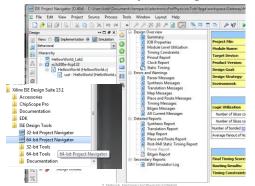

### "Gateway" lab exercises

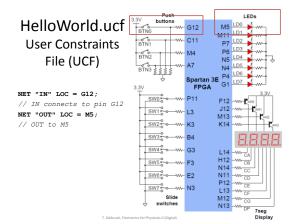

#### HellowWorld\_Lab1

HelloLotsofWorlds\_Lab2 HelloWorldSynchronous\_Lab3 ShiftingTheWorld\_Lab4 ShiftingManyWorlds\_Lab5 CountingTheWorld\_Lab6 TimingTheWorld\_Lab7 DecodingTheWorld\_Lab8 CountingInDecimal\_Lab9 ColouringTheWorld\_Lab10 WorldofStateMachines\_Lab11 LinkedStateMachine\_Lab12

Xilinx ISE Project Navigator

#### HelloWorld.v verilog hardware description language (HDL)

module HelloWorld(

input IN,

output OUT

);

assign OUT = IN;

endmodule

T. Delbruck, Electronics for Physicists II (Digital)

Delbruck, Electronics for Physicists II (Digit